この記事では,組み合わせ回路についてのメモを書いていく.

Turning Completeをプレイしているうちに自分の知識が足りないと感じ,勉強しました.

特に今回は,自分の知りたかった2入力ゲートと多入力ゲートの遅延について学べました.

この記事は,自分用のメモなので勉強したいならうさぎ先生ととり先生の計算機工学の動画を見るとよいと思います.

論理回路とゲート

論理回路

ブール演算を扱うための回路

ブール代数

2値論理を扱うための数学

中央処理装置(CPU)などは通常,論理回路で構成されている.

CPUでは処理が間に合わないときは,専用の論理回路を作ることも多い.

論理回路では,0と1を電圧の高低で表現する.

電源電圧の電圧値をHレベル,グラウンドの電圧値をLレベルという.

そして,Hレベルを論理値1,Lレベルを0とみなすのが正論理

Lレベルを論理値1,Hレベルを0とみなすのが負論理

という.

NOTゲートはインバータとよく呼ばれる

また,入力値をそのまま出力値とするゲートをバッファと呼ぶ.

最近の回路設計ではゲートなどを図で書かないでハードウェア記述言語(VHDL)を用いてテキストで記述することが多い.

NANDゲートとNORゲート

現在の技術では,ANDゲートやORゲートを直接作るのは難しい.

しかし,NANDゲート,NORゲートなら上記に比べ簡単に作ることができる.さらにNANDとNORは完全形である.そのため,NANDゲートとNORゲートは重宝される.(NANDは完全形かつNORはNANDの双対性があるからNORも完全形)

ここで,標準ロジックICと集積回路について説明する.

標準ロジックIC (昔)

1パッケージ内に配線されてない複数個のゲートが入っており,導線と半田で配線することで論理回路を作ることができる.

集積回路 (現在)

複数の部品を1チップに集積させた回路のこと.

チップは電子回路が詰まったシリコンの小さな部品で1チップの中に何百万~何十億ものトランジスタが詰め込まれている.

集積回路は標準ロジックとは違いゲートを置くのと同時に配線する.そして,あとから配線を変えることは不可能である.

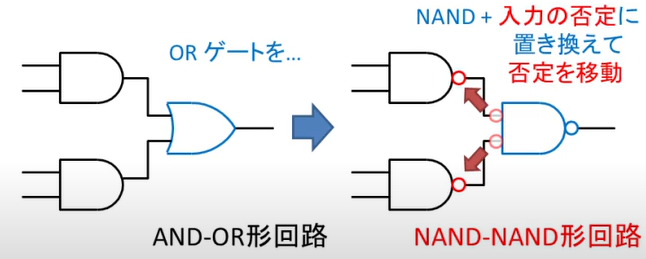

NAND-NAND形回路

AND-OR形(積和形)回路のAND.ORをNANDに置き換えても等価な回路になる.

NAND-NAND形が最適解だと思われていた時代もあったらしいが,現行の技術では最適解ではない.

このことについては,後の「ゲートの中身」の「複合ゲート」で触れる.

上の写真はNANDゲート – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

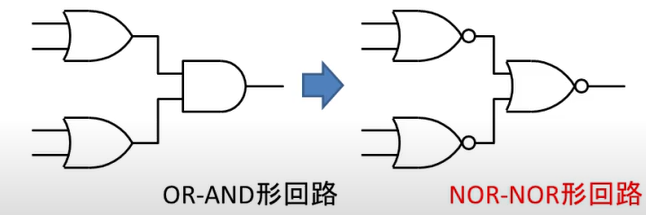

NOR-NOR形回路

OR-AND形(和積形)回路のOR,ANDをNORに置き換えても等価な回路になる.

上の写真はNANDゲート – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

ゲートとトランジスタ (重要)

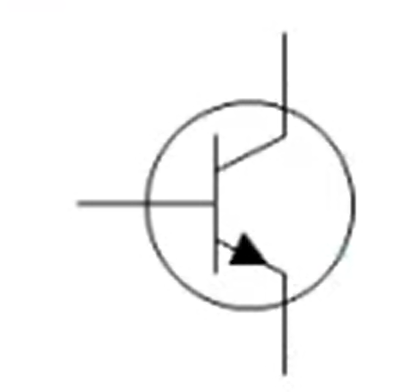

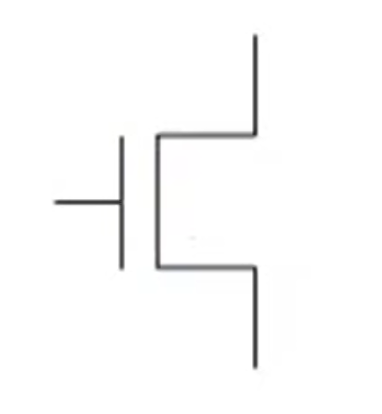

トランジスタの種類(2種類)

論理ゲートはトランジスタと呼ばれる素子からできている.

TTL回路では,バイポーラトランジスタが使われ,主席回路ではMOSFETトランジスタが使われている.

バイポーラトランジスタはうまく集積できなかった.MOSFETトランジスタはうまく集積化でき,集積回路で使われる.

左がバイポーラトランジスタで右がMOSFETトランジスタ

また,ムーアの法則というものがある.

ムーアの法則

半導体の集積密度は18~24か月で倍増するという法則(予測)

ゲートの中身

論理ゲートはトランジスタと呼ばれる素子のスイッチング動作を利用して作る.

入力がHのときにONになり,入力がLのときにOFFになるスイッチはnMOS

入力がHのときにOFFになり,入力がLのときにONになるスイッチはpMOS

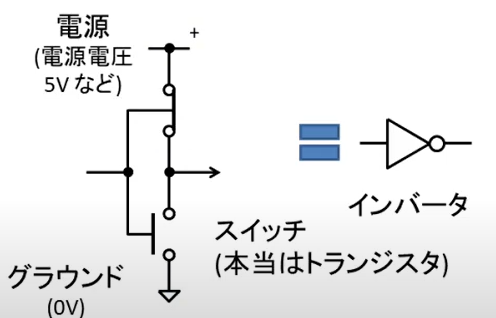

インバータ

インバータをスイッチで構成すると下のような写真になる.

論理ゲートではNANDに同じ入力を入力すれば出力できるが,実際の内部はNANDゲートではなくインバータだけの回路として,スイッチ(トランジスタ)を用いて構成される.

電源側のスイッチはpMOS,グラウンド側のスイッチはnMOS

もしHが入力されたら,電源側のpMOSスイッチがOFF,グラウンド側のnMOSスイッチがONになり出力がLになる.

Lが入力されたら,電源側のpMOSスイッチがON,グラウンド側のnMOSスイッチがOFFになり出力がHになる.

上の写真はゲートとトランジスタ – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

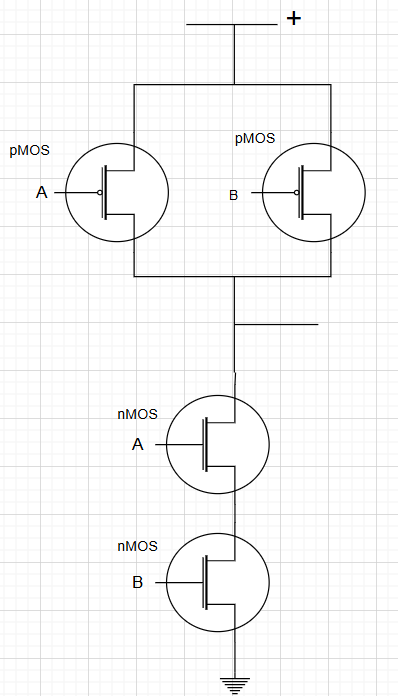

NANDゲート

トランジスタを直列につなげると両方がONなら導通する(論理積)

トランジスタを並列につなげると両方がOFFなら導通する(論理和)

それぞれ双対の関係にある.

NANDゲートは電源側にはグラウンドが側と双対な回路を設ける.

電源側には,入力がLのときONになるスイッチ(pMOS)をおく.

入力がLのときにONになるということは入力に否定をとるということでもある.

式で表すと以下になる.

z = (not A)+(not B)

グラウンド側には入力がHのときONになるスイッチ(nMOS)をおく.

導通したときにLになるため,全体に否定をとる.

式で表すと以下になる.

z = not(A・B)

2式は同じである.

つまり,電源側は出力が1がHに対応するときのNANDの動作(正論理)を表し,グラウンド側は出力が0がHに対応するときのNANDの動作(負論理)を表している.

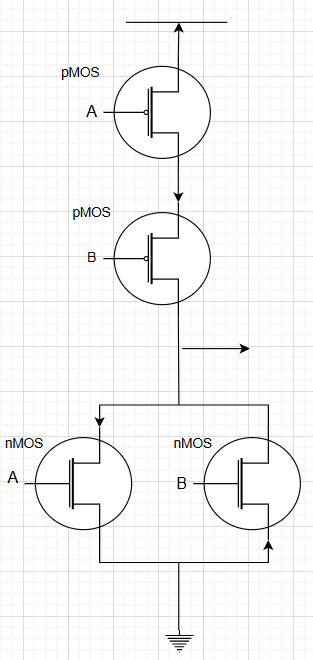

NORゲート

NORゲートは電源側にはグラウンドが側と双対な回路を設ける.

電源側には,入力がLのときONになるスイッチ(pMOS)をおく.

入力がLのときにONになるということは入力に否定をとるということでもある.

式で表すと以下になる.

z = (not A)・(not B)

グラウンド側には入力がHのときONになるスイッチ(nMOS)をおく.

導通したときにLになるため,全体に否定をとる.

式で表すと以下になる.

z = not(A+B)

2式は同じである.

つまり,電源側は出力が1がHに対応するときのNORの動作(正論理)を表し,グラウンド側は出力が0がHに対応するときのNORの動作(負論理)を表している.

ANDゲートとORゲート

現在の技術ではANDゲートやORゲートを直接作ることはできない.

電源側にnMOS,グラウンド側にpMOSを使うと作ることができそうだが,pMOSは電源側,nMOSはグラウンド側に接続しないとまともに動作しない.そのため,NANDゲートやORゲートの出力をNOTに入力すればANDゲートとORゲートを作ることができる.

複合ゲート

直列(論理積)と並列(論理和)を組み合わせることで複雑な論理式も1ゲートで実現できる.

複雑な論理式も1ゲートで実現できる.

- あらゆる単調減少関数を実現できる

- NOT,NAND,NORも単調減少関数 (AND,ORはしきい値関数で単調増加関数)

このようなゲートを複合ゲートと呼ぶ.

前述の「NANDゲートとNORゲート」の「NAND-NAND形」でNAND-NAND形は最適解ではないと述べた.これは,複合ゲートがあるためである.NANDの組み合わせは1ゲートで実現できる.

寄生容量

寄生容量

設計者が意図しない容量(コンデンサ)

・金属板でも線でも2つあればそれだけで容量発生する

・信号線や線に接続される部品などで発生

寄生抵抗や誘導も発生する.

集積回路では問題になるのは抵抗と容量.誘導はほとんど発生しない.集積回路の設計ではコイルは使えないと考えていい.

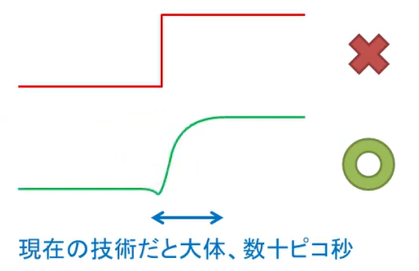

この寄生容量や寄生抵抗が原因で遅延が発生する.

ゲート出力の立ち上がりが滑らかになる.下の図

上の写真はゲートとトランジスタ – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

ゲートや信号線を通るごとに立ち上がり,立ち下りは徐々に遅れる

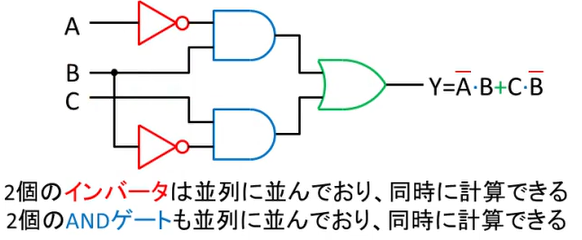

積和形の論理式を実現した論理回路のゲート段数は必ず3段以下

インバータ・ANDゲート・ORゲートの3段

計算時間もゲート3段分

上の写真はゲートとトランジスタ – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

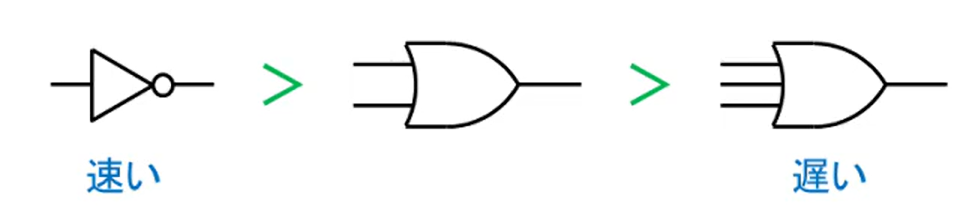

多入力ゲートの遅延 (ずっと知りたかったこと)

多入力ゲートと2入力を組み合わせて作った回路の論理式は等しいが回路としては別物である.

2入力ゲートを組み合わせたものより,多入力ゲートの方が動作は速い.

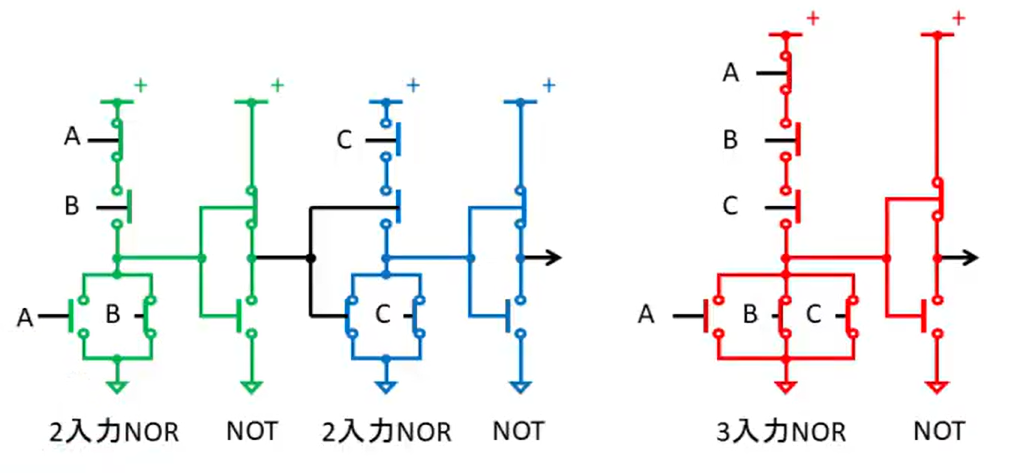

例えば,2入力のORを組み合わせて作ったものと3入力のORを組み合わせて作ったものをトランジスタにして考えると下のようになる.

左が4段,右が2段となり,3入力ORの方が速くなる.

上の写真はゲートとトランジスタ – 組み合わせ回路 – うさぎ先生ととり先生の計算機工学の動画中の画像から

ただ,注意してほしいのが多入力ゲートは2入力ゲート単体よりは遅い.

そして,2入力ゲートもインバータよりは遅い.

だが,計算時間はゲートの種類や入力数だけから決まるわけではない.

非常に多くの要因が絡むため,Turning Completeではそこまで考えなくてもいいと思った.

このことが分かったおかげで,自分の間違いに気づけた.

Turning CompleteでNANDが少なければ少ないほど動作が速くなると思っていたがそれは間違いであることに気づいた.

また,ゲートの段数以外にも下のような要因も計算時間に関係している.

ファンアウト

ファンアウト

ゲートの出力に接続されているゲートの数

ファンアウトが大きくなると寄生容量が大きくなり,速度が遅くなる.

大きすぎるとそもそも回路が動かなくなる.

その場合バッファを挿入するなどしてファンアウトを減らす必要がある.(遅くなる)

回路が動作する最大のファンアウトを”最大ファンアウト”と呼ぶ.最大ファンアウトはだいたい10くらいのことが多い

ブログを書く上で参考にしたもの

- うさぎ先生ととり先生の計算機工学の動画

- ChatGPT

コメント